[45] Date of Patent:

Dec. 10, 1985

| [54] | HIGH SPEED DATA COMPRESSION AND |

|------|---------------------------------|

|      | DECOMPRESSION APPARATUS AND     |

|      | METHOD                          |

[75] Inventor: Terry A. Welch, Concord, Mass.

[73] Assignee: Sperry Corporation, New York, N.Y.

[21] Appl. No.: 505,638

[22] Filed: Jun. 20, 1983

[51] Int. Cl.<sup>4</sup> ...... G06F 5/00

# [56] References Cited

#### U.S. PATENT DOCUMENTS

4,464,650 8/1984 Eastman ...... 340/347 DD

### OTHER PUBLICATIONS

Ziv, "IEEE Transactions on Information Theory", IT-24-5, Sep. 1977, pp. 530-537. Ziv, "IEEE Transactions on Information Theory", IT-23-3, May 1977, pp. 337-343.

Primary Examiner—Charles D. Miller Attorney, Agent, or Firm—Howard P. Terry; Albert B. Cooper

# [57] ABSTRACT

A data compressor compresses an input stream of data character signals by storing in a string table strings of data character signals encountered in the input stream. The compressor searches the input stream to determine

the longest match to a stored string. Each stored string comprises a prefix string and an extension character where the extension character is the last character in the string and the prefix string comprises all but the extension character. Each string has a code signal associated therewith and a string is stored in the string table by, at least implicitly, storing the code signal for the string, the code signal for the string prefix and the extension character. When the longest match between the input data character stream and the stored strings is determined, the code signal for the longest match is transmitted as the compressed code signal for the encountered string of characters and an extension string is stored in the string table. The prefix of the extended string is the longest match and the extension character of the extended string is the next input data character signal following the longest match. Searching through the string table and entering extended strings therein is effected by a limited search hashing procedure. Decompression is effected by a decompressor that receives the compressed code signals and generates a string table similar to that constructed by the compressor to effect lookup of received code signals so as to recover the data character signals comprising a stored string. The decompressor string table is updated by storing a string having a prefix in accordance with a prior received code signal and an extension character in accordance with the first character of the currently recovered string.

### 181 Claims, 9 Drawing Figures

```

SUBROUTINE COMP (IBUFA, NA, IBUFB, NB)

2.

3.

C PURPOSE

4.

C

CONVERT CONSECUTIVE 9 BIT STRINGS TO CONSECUTIVE 12 BIT STRINGS

5.

C USAGE

CALL COMP (IBUFA, NA, IBUFB, NB)

6.

INPUT

7.

IBUFA = INPUT BUFFER CONTAINING CONSECUTIVE 9 BIT STRINGS.

δ.

C

9.

= NO. OF CONSECUTIVE 9 BIT STRINGS STARTING AT IBUFA.

C

NA

10.

OUTPUT

C

IBUFB = OUTPUT BUFFER CONTAINING CONSECUTIVE 12 BIT STRINGS.

11.

C

12.

C

= NO. OF CONSECUTIVE 12 BIT STRINGS STARTING AT IBUFB.

13.

C

DIMENSION IBUFA(1), ITABLE(4096), IBUFB(1)

14.

15.

DATA IFILL /512/

NCHA=1

@ INPUT CHARACTER COUNT

16.

@ OUTPUT INDEX

17.

NB =1

DO 10 I=1, 4096

10.

10 ITABLE(1)=IFILL

19.

20.

NODENO=IBITSG (IBUFA(1), 9, 1)

21.

100 NCHA=NCHA+1

IF (NCHA .GT. NA) 60 TO 4GO

22.

NOWCHR=IBITSG (IBUFA(1), 9, NCHA)

23.

24.

LOC=XOR((511-NOWCHR)+8, NODENO)+1

25.

N=1

120 IF (LOC .LE. 513) 60 TO 180

20.

IF (ITABLE(LOC) .NE. NODENO) GO TO 130

27.

23.

NODENO=LOC-1

29.

60 TO 100

130 IF (ITABLE(LOC) .EQ. IFILL) GO TO ZOO

30.

31.

180 N=N+1

32.

IF (N .GT. 7) 60 TO 300

LOC=MOD(xOR(2+NODENO, 1365)+LOC-1, 4096)+1

33.

60 TO 120

34.

35.

200 ITABLE(LOC)=NODENO

300 CALL IBITSP (IBUFB(1), 12, NB, NODENO)

36.

37.

NODENO=NOWCHR

38.

NB=NB+1

GO TO 100

39.

40.

400 CALL IBITSP (IBUFB(1), 12, NB, NODENO)

RETURN

41.

42.

END

```

```

SUBROUTINE DECOMP' (IBUFB, NB, IBUFA, NA)

2.

C

CONVERT CONSECUTIVE 12 BIT STRINGS TO OUTPUT BIT STRINGS

3.

C

IBUFB = INPUT BUFFER CONTAINING CONSECUTIVE 12 BIT STRINGS.

4.

C

# NO. OF CONSECUTIVE 12 BIT STRINGS STARTING AT IBUFB.

5.

C

C

* OUTPUT BUFFER CONTAINING CONSECUTIVE NBITSA BIT

IBUFA

6.

7.

C

STRINGS

= NO. OF CONSECUTIVE NBITSA BIT STRINGS STARTING AT

C

8.

IBUF.A.

9.

DIMENSION IBUFB(1), ITABLE(4096), IBUFA(1)

10.

DATA NBITSA /9/

11.

NCHB=1

12.

NA=1.

13.

DO 10 I=1, 4096

14.

15.

10 ITABLE(I)=0

NOCODE=IBITSG(IBUFB(1), 12, NCHB)

16.

ICHAR=NOCODE

17.

CALL IBITSP (IBUFA, NBITSA, NA, ICHAR)

18.

19.

NODOLD=NOCODE

20.

LEVOLD=1

21.

100 NCHB=NCHB+1

IF (NCHB .GT. NB) GO TO 510

22.

NODENO=IBITS6(IBUFB(1), 12, NCHB)

23.

24.

NOCODE=NODENO

IF (NODENO .SF. 512) 60 TO 120

25.

26.

LEVEL=C

GO TO 210

120 IF (ITABLE(NODENO+1) .NE. 0) GO TO 130

27.

28.

29.

LEVEL=LEVOLD

CALL IBITSP (IBUFA, NBITSA, NA+LEVEL+1, ICHAR)

30.

31.

NODENO=NODOLD

32.

60 TO 200

130 LEVEL=BITS(ITABLE(NODENO+1), 13, 12)

33.

200 IF (NODENO .LE. 512) 60 TO 210

34.

INDEX=BITS(ITABLE(NODENO+1), 13, 12)

ICHAR=BITS(ITABLE(NODENO+1), 25, NRITSA)

35.

36.

CALL IBITSP (IBUFA, NBITSA, INDEX+NA+1, ICHAR)

37.

NODENO=BITS (ITABLE (NODENO+1), 1, 12)

38.

39.

60 TO 200

40.

210 ICHAR=NODENO

CALL IBITSP (IBUFA, NBITSA, NA+1, ICHAR)

41.

42.

N=1

LOC=XOR((511-ICHAR)+8, NODOLD)+1

43.

44.

215 IF (LOC .LE. 513) 60 TO 218

IF (ITABLE(LOC) .EQ. 0) 60 TO 220

45.

46.

218 N=N+1

IF (N .GT. 7) 60 TO 225

47.

LOC=MOD(XOR(2*NODOLD, 1365)+LOC-1, 4096)+1

48.

49.

60 TO-215

220 BITS(ITABLE(LOC), 1, 12)=NODOLD

5ü.

BITS(ITABLE(LOC), 25, NBITSA)=ICHAR

51.

BITS(ITABLE(LOC), 13, 12)=LEVOLD

52.

225 NODOLD=NOCODE

53.

LEVOLD=LEVEL+1

54.

55.

NA=NA+LEVEL+1

56.

60 TO 100

510 RETURN

57.

58.

END

```

```

FUNCTION IBITSG (IBUF, NPERBY, NTHBY)

2

С

3

C PUPPOSE

RETRIEVE A BYTE FROM A SEQUENCE OF BYTES OF THE SAME LENGTH

C

5

C USAGE

IBYTE = IBITSG (IBUF, NPEPHY, NTHBY)

C

INPUT

3

= BUFFER CONTAINING CONSECUTIVE BYTES OF NPERBY BITS

9

C

EACH'.

10

NPERBY = NO. OF BITS PER BYTE (1-36).

11

C

NTHBY -= INDEX OF BYTE POSITION WHERE BYTE IS TO BE RETRIEVED

12

C

FROM. THE FIRST BYTE POSITION IS 1.

13

С

OUTPUT

IBYTE : = WORD CONTAINING THE SYTE RETRIEVED IN THE LOW-ORDER

14

C

15

C

NPERBY BITS.

16

C REMARKS

17

C

USE SUBROUTINE IBITSP FOR STORAGE.

18

C METHOD

19

C

SEE CODE.

20

21

DIMENSION IBUF(1)

22

DATA NPERMO /36/

23

NaIT1=(NTHBY-1) *NPERBY+1

NWEASE=(NBIT1-1)/NPERWD

25

NBITA=NBITT-NWBASE*NPERWD

26

NBITE=NBITA+NPEREY-1

27

IF (NBITS .GT. NPERWD) GO TO 13

IBYTE=BITS(IBUF(NWBASE+1), NBITA, NPERBY)

28

29

30

GO TO 20

10 NMOVEZ=NEITS-NPERWD

31

ISYTE=BITS(IBUF(NWBASE+2), 1, vMOVEZ)

32

VMOVE1 = NPERSY-NMOVE2

33

BITS (IBYTE, APERWD+1-MPERBY, MMOVE1) =

34

* BITS (IBUF(NWBASE+1), NBITA, NMOVE1)

35

37YSI=DZTIEI 05

36

RETURN

37

END

```

```

SUBROUTINE IBITSP (IBUF, NPERBY, NTHEY, IBYTE)

2

C

3

C PURPOSE

STORE A BYTE IN A SEQUENCE OF BYTES OF THE SAME LENGTH

C

C USAGE

C

CALL IBITSP (IBUF, NPERBY, NTHBY, 18YTE)

7

C

INPUT

C

= BUFFER CONTAINING CONSECUTIVE BYTES OF NPERBY BITS

å

9

€.

EACH.

C

NPERBY = NO. OF BITS PER BYTE (1-36).

10

= INDEX OF BYTE POSITION IN IBUF WHERE BYTE IS TO BE

11

C

YEHTA

THE FIRST SYTE POSITION IS 1.

C

12

STORED.

13

C

= WORD CONTAINING THE BYTE TO BE STORED IN THE LOW-ORDER

C

14

NPERBY BITS.

15

¢

OUTPUT

= UPDATED BUFFER WITH THE LOW-ORDER NPERBY BITS OF IBYTE

16

C

IBUF

17

STORED IN THE NTHBY BYTE POSITION.

C REMARKS

18

19

C

USE FUNCTION IBITSG FOR RETRIEVAL.

20

C METHOD

21

C

SEE CODE.

22

С

23

DIMENSION IBUF(1)

24

DATA NPERWO /36/

25

NBIT1=(NTHBY-1)*NPERBY+1

NWBASE=(NEIT1-1)/NPERWD

26

27

NBITA=NBIT1-NWBASE*NPERWD

28

NBITB=NBITA+NPERBY-1

29

IF (NBITB .GT. NPEP#D) GO TO 10

30

BITS (IBUF (NWBASE+1), NBITA, MPEREY) = IBYTE

31

RETURN

32

10 NMOVEZ=NEITS-NPEPWD

33

BITS(IBUF(N#BASE+2), 1, NMOVE2)=BITS(IBYTE, NPERWD+1-N*OVE2,

* * MOVES)

34

35

NMOVE1=NPERBY-NMOVE2

36

BITS(IBUF(NWBASE+1), NBITA, NMOVE1) =

37

* airs (layre, MPERWD+1-MPEPEY, MYOVE1)

38

RETURN

END

```

### HIGH SPEED DATA COMPRESSION AND DECOMPRESSION APPARATUS AND METHOD

#### BACKGROUND OF THE INVENTION

1. Field of the Invention

The invention relates to the field of data compression and decompression (recovery) of the compressed data.

2. Description of the Prior Art

Data compression systems are known in the prior art 10 that encode a stream of digital data signals into compressed digital data signals and decode the compressed digital data signals back into the original data signals. Data compression refers to any process that converts data in a given format into an alternative format having 15 fewer bits than the original. The objective of data compression systems is to effect a savings in the amount of storage required to hold or the amount of time required to transmit a given body of digital information. The compression ratio is defined as the ratio of the length of 20 the encoded output data to the length of the original input data. The smaller the compression ratio, the greater will be the savings in storage or time. By decreasing the required memory for data storage or the required time for data transmission, compression results 25 in a monetary savings. If physical devices such as magnetic disks or magnetic tape are utilized to store the data files, then a smaller space is required on the device for storing the compressed data thereby utilizing fewer disks or tapes. If telephone lines or satellite links are 30 utilized for transitting digital information, then lower costs result when the data is compressed before transmission. Data compression devices are particularly effective if the original data contains redundancy such as having symbols or strings of symbols appear with high 35 frequency. A data compression device transforms an input block of data into a more concise form and thereafter translates or decompresses the concise form back into the original data in its original format.

For example, it may be desired to transmit the con- 40 tents of a daily newspaper via satellite link to a remote location for printing thereat. Appropriate sensors may convert the contents of the newspaper into a data stream of serially occurring characters for transmission via the communication link. If the millions of symbols 45 comprising the contents of the newspaper were compressed before transmission and reconstituted at the receiver, a significant amount of transmission time would be saved.

As a further example, when an extensive data base 50 and so cannot be utilized for general purpose usage. such as an airline reservation data base or a banking system data base is stored for archival purposes, a significant amount of storage space would be saved if the totality of characters comprising the data base were compressed prior to storage and reexpanded from the 55 stored compressed files for later use.

To be of practical and general utility, a digital data compression system should satisfy certain criteria. The system should provide high performance with respect to the data rates provided by and accepted by the equip- 60 ment with which the data compression and decompression systems are interfacing. The rate at which data can be compressed is determined by the input data processing rate into the compression system, typically in millions of bytes per second (megabytes/sec). High perfor- 65 mance is necessary to maintain the data rates achieved in present day disk, tape and communication systems which rates typically exceed one megabyte/sec. Thus,

the data compression and decompression systems must have data bandwidths matching the bandwidths achieved in modern devices. The performance of prior art data compression and decompression systems is typically limited by the speed of the random access memories (RAM), and the like, utilized to store statistical data and guide the compression and decompression processes. High performance for a compression device is characterized by the number of ram cycles (read and write operations) required per input character into the compressor. The fewer the number of memory cycles, the higher the performance. A high performance design can be utilized with economical, slow RAMS for low speed applications such as telephone communications, or with very fast RAMS for magnetic disk transfers.

Another important criterion in the design of a data compression and decompression system is compression effectiveness. Compression effectiveness is characterized by the compression ratio of the system. The compression ratio is the ratio of data storage size in compressed form divided by the size in uncompressed form. In order for data to be compressible, the data must contain redundancy. Compression effectiveness is determined by how effectively the compression procedure matches the forms of redundancy in the input data. In typical computer stored data, e.g. arrays of integers, text or programs and the like, redundancy occurs both in the nonuniform usage of individual symbology, e.g. digits, bytes, or characters, and in frequent recurrence of symbol sequences, such as common words, blank record fields, and the like. An effective data compression system should respond to both types of redundancy.

A further criterion important in the design of data compression and decompression systems is that of adaptability. Many prior art data compression procedures require prior knowledge, or the statistics, of the data being compressed. Some prior art procedures adapt to the statistics of the data as it is received. Adaptability in the prior art processes has required an inordinate degree of complexity. An adaptive compression and decompression system may be utilized over a wide range of information types, which is typically the requirement in general purpose computer facilities. It is desirable that the compression system achieves good compression ratios without prior knowledge of the data statistics. Data compression and decompression procedures currently available are generally not adaptable

Another important criteria in the design of data compression and decompression systems is that of reversibility. In order for a data compression system to possess the property of reversibility, it must be possible to reexpand or decompress the compressed data back into its original form without any alteration or loss of information. The decompressed and the original data must be identical and indistinguishable with respect to each other.

General purpose data compression procedures are known in the prior art that either are or may be rendered adaptive, two relevent procedures being the Huffman method and the Tunstall method. The Huffman method is widely known and used, reference thereto being had in an article by D. A. Huffman entitled "A Method for the Construction of Minimum Redundancy Codes", Proceedings IRE, 40, 10, pages 1098-1100 (September, 1952). Further reference to the

Huffman procedure may be had in an article by R. Gallagher entitled "Variations on a Theme by Huffman, IEEE Information Theory Transactions, IT-24, No. 6 (November, 1978). Adaptive Huffman coding maps fixed length sequences of symbols into variable length 5 binary words. Adaptive Huffman coding suffers from the limitation that it is not efficacious when redundancy exists in input symbol sequences which are longer than the fixed sequence length the procedure can interpret. the input sequence lengths rarely exceed 12 bits due to RAM costs and, therefore, the procedure generally does not achieve good compression ratios. Additionally, the adaptive Huffman procedure is complex and often requires an inordinately large number of memory 15 cycles for each input symbol. Thus, the adaptive Huffman procedure tends to be undesirably cumbersome, costly, and slow thereby rendering the process unsuitable for most practical present day installations.

Reference to the Tunstall procedure may be had in 20 the doctoral thesis of B. T. Tunstall, entitled "Synthesis of Noiseless Compression Codes", Georgia Institute of Technology, (September, 1967). The Tunstall procedure maps variable length input system sequences into fixed length binary output words. Although no adaptive 25 version of the Tunstall procedure is described in the prior art, an adaptive version could be derived which, however, would be complex and unsuitable for high performance implementations. Neither the Huffman nor the Tunstall procedure has the ability to encode increas- 30 to provide highest performance. ingly longer combinations of source symbols.

A further adaptive data compression and decompression system that overcomes many of the disadvantages of the prior art is that disclosed in co-pending U.S. patent application Ser. No. 291,870 filed Aug. 10, 1981 35 now U.S. Pat. No. 4,464,650 entitled "Apparatus and Method for Compressing Data and Restoring the Compressed Data" by M. Cohen, W. Eastman, A. Lempel and J. Ziv. The procedure of said Ser. No. 291,870 parses the stream of input data symbols into adaptively 40 growing sequences of symbols. The procedure of said Ser. No. 291,870 suffers from the disadvantages of requiring numerous RAM cycles per input character and utilizing time consuming and complex mathematical procedures such as multiplication and division to effect 45 FIG. 2. compression and decompression. These disadvantages tend to render the procedure of said Ser. No. 291,870 unsuitable for numerous economical high performance implementations.

It is appreciated from the foregoing that neither the 50 in the programs of FIGS. 6 and 7. prior art nor the procedure of said Ser. No. 291,870 provides an adaptive, efficient, compression and decompression system suitable for high performance applications. No known prior design approach is directly suitable for such a device.

## SUMMARY OF THE INVENTION

The present invention overcomes the disadvantages of the above described systems by providing an economical, high performance, adaptable and reversible 60 data compression and decompression system and method that achieves good compression ratios. The present invention compresses a stream of data character signals into a compressed stream of code signals by storing strings of data character signals parsed from the 65 input data stream and searching the stream of data character signals by comparing the stream to the stored strings to determine the longest match therewith. The

compression apparatus also stores an extended string comprising the longest match from the stream of data character signals extended by the next data character signal following the longest match. When the longest match is extended and stored, a code signal corresponding to the stored extended string is assigned thereto. The compressed stream of code signals is provided from the code signals corresponding to the stored longest matches. A stored string of data characters is comprised In practical implementations of the Huffman procedure, 10 of a prefix string and the extension character. A string is stored in terms of the code signal corresponding to its prefix string.

The compressed stream of code signals is decompressed by constructing and storing character strings comprising prefix code signals and extension character signals. The decompression system stores a string in accordance with a received code signal and the extension character which is received as the first character of the next following string.

The strings of data character signals are entered into storage by means of a limited search hashing technique that provides a limited number of hash addresses for each search iteration.

# BRIEF DESCRIPTION OF THE DRAWINGS

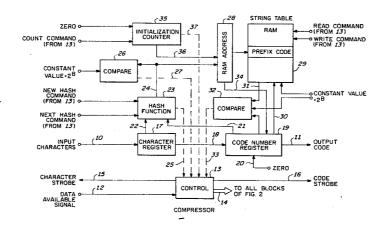

FIG. 1 is a schematic representation of a parsed portion of a stream of data character signals.

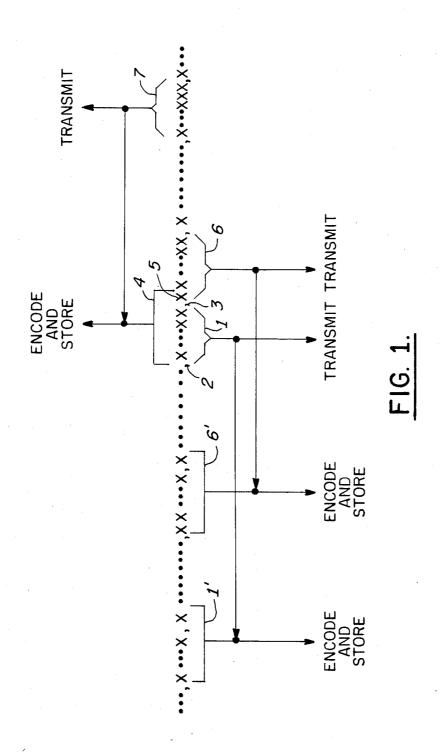

FIG. 2 is a schematic block diagram of a data compressor in accordance with the invention implemented

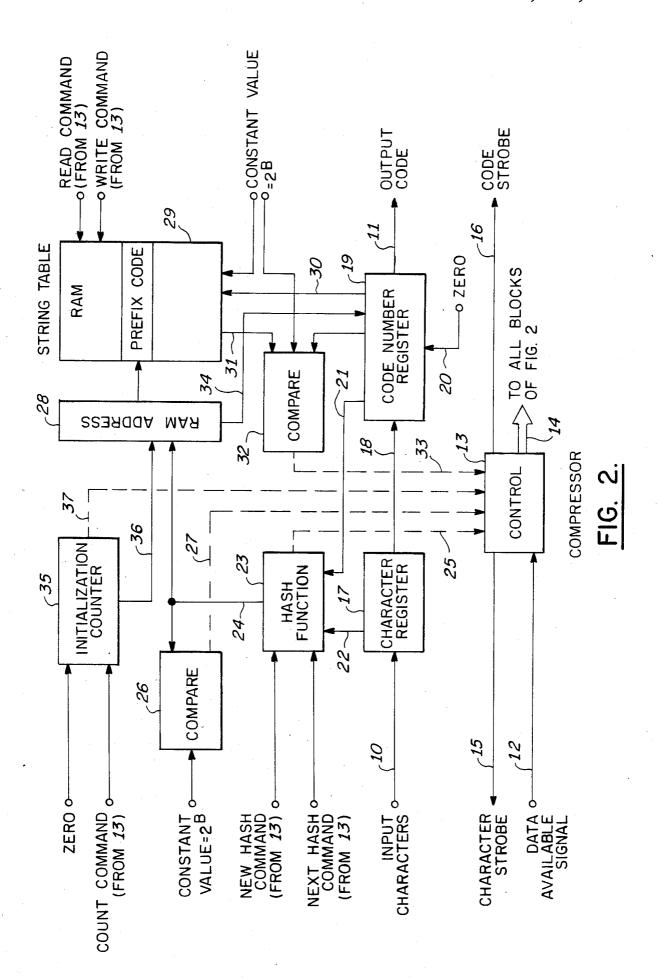

FIG. 3 is a schematic block diagram of a data decompressor in accordance with the invention implemented to provide highest performance and adapted to decompress the compressed stream of code signals from the compressor of FIG. 2.

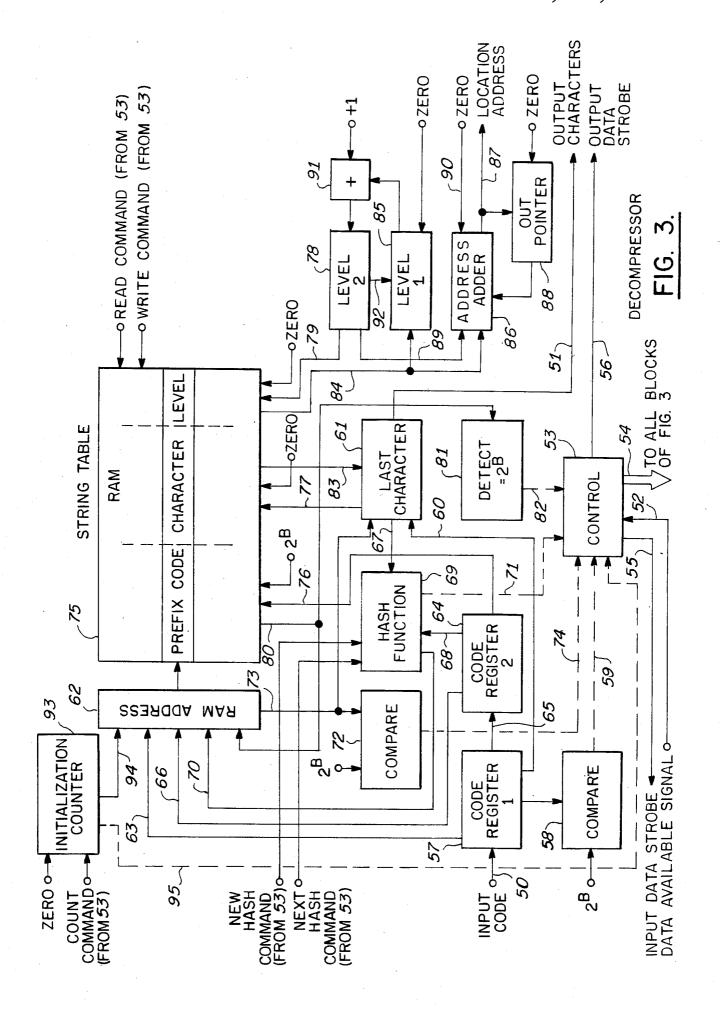

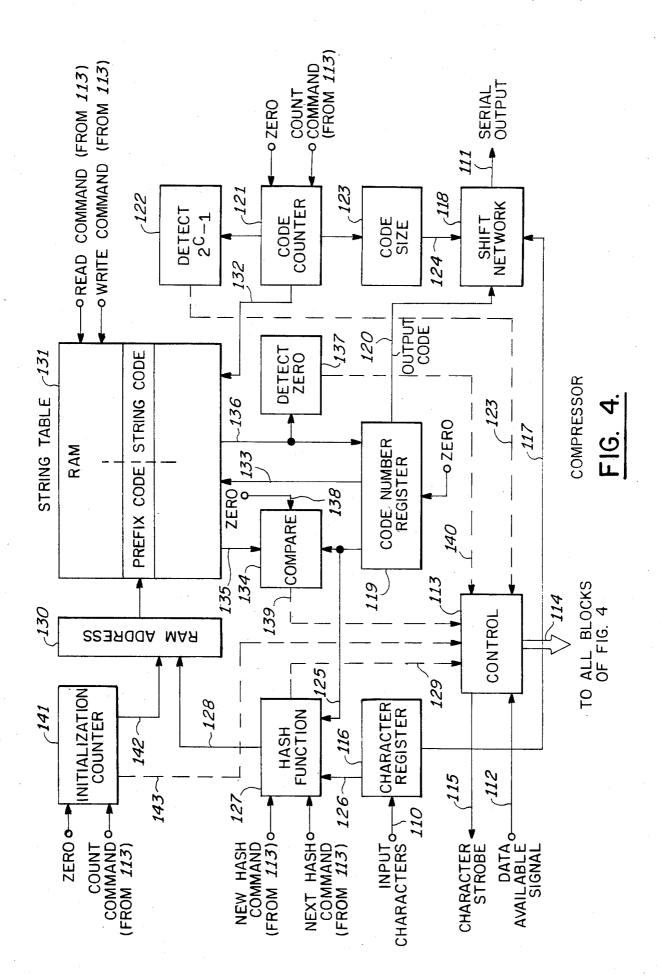

FIG. 4 is a schematic block diagram of a data compressor in accordance with the invention implemented to provide highest compression.

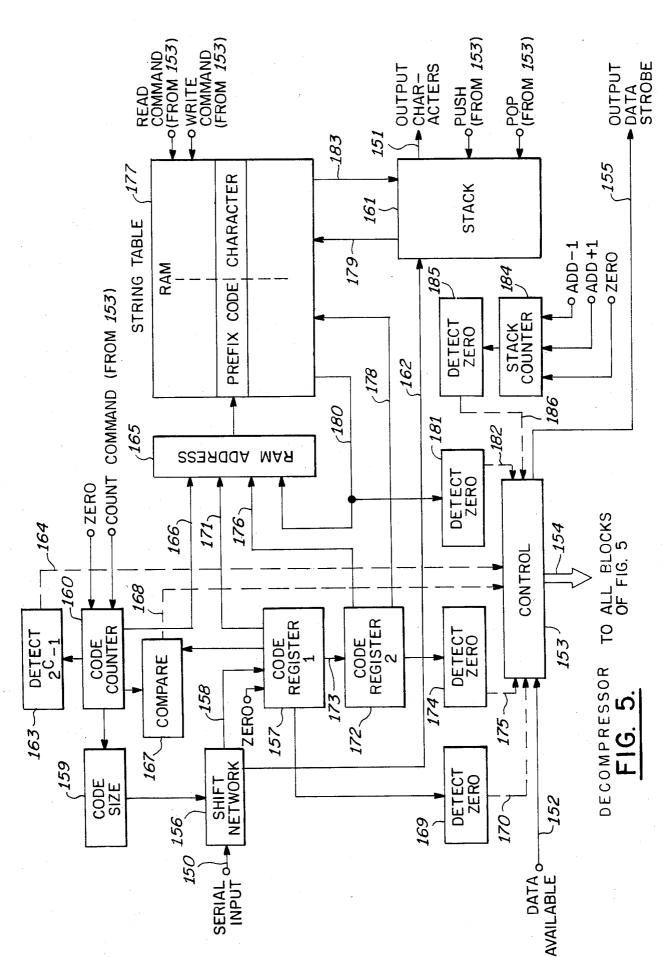

FIG. 5 is a schematic block diagram of data decompressor in accordance with the invention implemented to decompress the compressed stream of code signals from the compressor of FIG. 4.

FIG. 5 is a listing of a Fortran subroutine for implementing in software a data compressor similar to that of

FIG. 7 is a listing of a Fortran subroutine for implementing in software a data decompressor similar to that of FIG. 3.

FIG. 8 is a listing in Fortran of a subroutine utilized

# DESCRIPTION OF THE PREFERRED **EMBODIMENTS**

The present invention comprises a data compressor 55 for compressing a stream or sequence of digital data character signals and providing a corresponding stream of compressed digital code signals. The invention further includes a decompressor for receiving the compressed code signals and restoring the original digital data. The data to be compressed may comprise, for example, English language textual material, stored computer records and the like. It is appreciated in present day data processing and communication systems that the characters of the alphabets over which compression is to be effected are processed and conveyed as bytes of binary digits in a convenient code such as the ASCII format. For example, input characters may be received in the form of eight-bit bytes over an alphabet of 256

characters. The compressed code signals from the compressor may either be stored in electronic storage files for, for example, archival purposes or may be transmitted to remote locations for decoding thereat. Additionally, an electronic storage file, such as a disk store, may include a compressor in its input electronics and a decompressor in its output electronics whereby all data entering the file is compressed for storage and all data retrieved from the file is decompressed before transmission to the utilization equipment. The prior art compres- 10 sion and decompression systems discussed above do not provide the performance or adaptability to accommodate such usage of compression and decompression. The high performance adaptive systems implemented in accordance with the present invention may be so uti- 15 lized.

A number of design options are usable in embodiments of the present invention in various combinations in accordance with the data to be compressed and the desired characteristics of the system. Three embodiments of the invention will be described; one embodiment combining the options to provide the highest performance, the second embodiment combining the options to provide the highest compression, and the third embodiment providing a programmed computer version of the highest performance embodiment.

The compressor of the present invention parses the input stream of data characters into strings or segments and transmits a code signal identifying each string. Except for data characters that are encountered for the 30 first time by the compressor, each parsed string comprises the longest match to a previously recognized string. The compressor transmits the code signal corresponding to the recognized string. When a string of characters is parsed from the input data stream, the 35 parsed string is extended by the next occuring character in the input stream to form an extended string which is encoded and stored in the compressor to be utilized for later encodings. Thus the character sequences which are recognized are constantly growing in average 40 length as statistical information is gathered in the course of compressing a block of data. The extension character is utilized as the first character in the next parsing iteration. The parsing is achieved in a single pass through the data, starting from the begining character and separat- 45 ing off one character at a time. Each string therefore, except for single character strings, is stored as a prefix string, which matches a previously stored string and the extension character. Each such string is conveniently stored in terms of the code signal representation of the 50 prefix with an actual or implied representation of the extension character. Parsing may be conceptualized as inserting virtual commas between the characters of the data stream thereby setting off the parsed strings or segments. Therefore, in the present invention the search 55 into the unprocessed data stream for a match involves searching from a comma to one character beyond the next ensuing comma to find the longest match with a previously observed string.

Referring to FIG. 1, a schematic representation of a 60 portion of a stream data characters is illustrated where the "X's" represent arbitrary characters of the alphabet. Commas are illustrated in the data stream only to depict the parsing. A string 1 of the data stream is parsed by virtual commas 2 and 3. The string 1 matches the previous string 1' and the string 1' is the longest extended string preceeding the comma 2 that matches the input data stream following the comma 2. The string 1' had

been previously encoded and the code therefore is transmitted by the compressor when encountering the string 1. The compressor then encodes and stores an extended string 4 comprising the prefix string 1 and an extension character 5. The extension character is the next character in the data stream following the prefix 1 irrespective of what character it is. In other words, the extension character 5 may be a character that has been seen previously in the data stream or it may be a character of the alphabet that is encountered for the first time.

The compressor starts the next parsing iteration at the virtual comma 3 starting with the extension character 5 until another longest match is achieved. Thus a string 6 is parsed that matches a previously extended string 6'. Again, as in the previous iteration, the code signal for the string 6' is transmitted and the string 6 extended by the next following character and the extended string encoded and stored. In a subsequent parsing iteration, a string 7 is parsed which matches the encoded and stored string 4. The code signal transmitted in this parsing iteration is that assigned to the extended string 4.

As discussed above, the code signals provided by the compressor may be stored or transmitted for subsequent decompression. The decompressor stores the data in terms of encoded prefix strings and extension characters. Thus, the decompressor constructs an entry in its storage comprising a received code signal and an extension character. For example, with continued reference to FIG. 1, when the decompressor receives the code signal associated with the string 1, the characters comprising the string are reconstructed, in a manner to be described in detail hereinbelow, by reason of the decompressor having previously constructed and stored the string 1'. In the next following iteration, when the decompressor receives the code signal associated with the string 6, the characters comprising the string are retrieved. At this point, the decompressor has received the code signal from the string 1 and has retrieved the extension character 5 and can thus construct and store the string 4 in a manner to be described in detail hereinbelow.

In the present invention, sequences of input bytes are compressed into code signals which may be of fixed or variable length depending upon the embodiment. As discussed above, input byte sequences are assigned code identifiers and whenever a sequence is reencountered in the input data stream, the same identifier is again transmitted. One-byte sequences are assigned codes and whenever a sequence is reencountered, it is extended by one byte and a new code assigned to the extended sequence. Conceptually, the compressor begins each data block with only the null string in the stored set. The compressor enters one-character strings in the set each time a new character is encountered and then utilizes these stored one-character strings to build longer strings. As each string is added to the set, it is assigned a code signal. Each time a character string from the input is found in the set, the next input character is appended to that string and the set searched to determine if the extended string is in the set. If the extended string is not already there, it is entered. Optionally, the string set can be initialized to include all single character strings. This may yield a higher performance implementation, but may lose some compression efficiency. The output code signals from the compressor may be considered as citations pointing to the previous occurance of an identical character sequence.

In the data compression and decompression system of said Ser. No. 291,870 an extension character is appended to each recognized sequence and the extended sequence encoded. The encoded representation of the extended sequence was transmitted by the compressor 5 as its compressed code. The compressor of the present invention, instead, stores the extended sequence and transmits the code for the recognized sequence. The recognized sequence is the prefix of the extended sequence. The stored extended sequence is then utilized 10 for later encoding. This alteration of the procedure of said Ser. No. 291,870 effects a substantial simplification of the data compression and decompression system by eliminating the time consuming and cumbersome mathematical manipulations utilized in said Ser. No. 291,870 15 and the concomitant hardware such as multiplication and division devices. The alteration, as well as effecting a substantial increase in device performance, also effects an increase in compression efficiency with typically encountered data. This is because in the system of said 20 Ser. No. 291,870, the extension character that is transmitted as part of the compressed code signal contains a number of bits commenserate with all symbols of the alphabet being equally likely. In the present invention, the extension character is transmitted as part of the 25 following compressed string code and, therefore, requires a smaller number of bits in accordance with the compression effected on the strings of characters.

The present invention utilizes a limited search length, calculated address hashing system to enter springs into 30 the string table and to search for strings in the string table. The hashing function utilizes a hash key comprised of a prior code signal and an extension character to provide a set of N hash table addresses where N is typically 1 to 4. The N RAM locations are sequentially 35 searched and if the item is not in the N locations, it is considered not to be in the table. In compression, if a new key to be inserted in the table cannot be accepted in the N assigned locations, it is omitted from the table. This limited search hashing procedure slightly reduces 40 compression efficiency but substantially increases implementation simplicity. Alternative embodiments may be utilized wherein the N hash addresses are searched in parallel in replicated RAMS.

The present invention may be implemented utilizing 45 fixed or variable length compressed code signals. A fixed length code signal embodiment results in implementation simplification with a slight loss in compression efficiency. A fixed length code embodiment tends to reduce RAM space requirements and the code shifting mechanism complexities necessitated by a variable code length implementation. The fixed length code implementation, however, is desirable when effecting a very high performance implementation.

Generally, the present invention effects compression 55 by mapping variable strings of input character signals into output code symbol signals. The compressor stores, in a string table (RAM) a list of strings it recognizes and for each string a corresponding output code signal. The set of strings so stored is constructed so that any sequence of input characters can be parsed into a stored string and hence can be mapped into an output code. Parsing is achieved at any iteration by consuming all consecutive input characters which match the longest string in the string table and transmitting the corresponding output code. The longest match is extended by the next input character, stored in the string table, and assigned a corresponding code.

8

Thus, the composition of the set of strings in the string table adapts to and is a statement of the current data block statistics. Specifically, each string added to the set is a one-character extension of a string already in the set. A string is added to the set only after it is actually observed in the input data. Therefore, a long string can occur in the set only if it has been often encountered and thus can be expected to recur frequently. The string set is stored as a table, preferably, in a random access memory (RAM). The strings are stored in what might be considered a linked-tree structure. Each string is stored, at least impliedly, with its code symbol, the last character of the string and the code symbol of the string prefix which contains all the string characters but the last. The decompressor in decoding a string utilizes multiple RAM accesses as each character is obtained individually and each prefix code is accessed in sequence.

The data signals are stored in the string table in a manner to facilitate locating the longest match for an input character sequence. As each input character is read, it is appended to a string already recognized (starting with the null string at the beginning of a new sequence), and the new string is tested to determine if it is in the table. If it is located in the table, its code is retrieved and the process is repeated with a new character and the new code. To so access the strings, they are conveniently identified by the tuple "Prefix code, extension character". A limited search hasing system is utilized to effect the search through the string table.

A hashing system usable in implementing the present invention comprises a function

hash (code, character)→address 1, address 2, . . .

which generates for a code, character combination a sequence of memory addresses. When inserting a string in the table, the generated RAM addresses are accessed in sequence until an empty site is found, and the item is inserted at that point. When retrieving an item, the same address sequence is accessed until the item is found or an empty site is found, in which case, the item is defined as not existing in the table. At each occupied site, the identifying code, character tuple for that string may be compared to determine if the site occupant is the desired item. For reasons to be described, it is actually only necessary in the present embodiments to compare the identifying code.

In the hash function employed in the present invention, the number of addresses derived and utilized is limited to a small fixed value N, where N is typically where one to four. If an item cannot be inserted in the string table in N accesses, the item is not utilized. If an item to be retrieved from the table is not located in N accesses, it is defined as not being in the table. This limited search aspect results in a small loss of compression efficiency, but a substantial increase in performance. The present invention will be described as effecting compression over an alphabet of B bit bytes. The hash function utilized in implementing the present invention is designed so that the set of addresses associated with any one code, all N addresses for all  $2^B$  extension characters, does not contain any address twice. Thus, when an address is accessed for a particular code, character tuple, comparison of the code is sufficient to establish the identity of the occupant of that location. It is not necessary to store the character value in the RAM. RAM space is thus conversed by reason of this

aspect of the hash function. Additionally, the hash function is designed so that abnormally heavy usage of consecutive values of codes or characters does not result in overuse of any particular set of addresses. This is achieved by assuring, when possible, that any two code, 5 character tuples having the same first address value will not have the same second address value. It will be appreciated that the several addresses generated by the hash function may be provided in parallel so that duplicate copies of the RAM may be searched concurrently 10 to further enhance performance of the system. Many hash functions that satisfy the above described criteria will perform satisfactorily in embodying the present invention and a particular, suitable hash function will be described hereinbelow. It is appreciated that other hash 15 functions satisfying the above criteria may be routinely

In the embodiments of the invention to be hereinbelow described, the output code signal from the compressor will have a nominal word length of C bits where 2<sup>C</sup> is less than or equal to the size of the string table. However, when the string table is first being constructed, fewer than C bits are required to select each string from those available during an iteration. Highest compression is achieved if progressively larger output codes are transmitted up to the limit of C bits. This approach utilizes additional output hardware to align the variable codes into fixed byte orientation. The output word length may also vary in accordance with the 30 recognition of new input characters. In one of the embodiments described below, whenever an input character is first encountered, the nullstring code is provided followed by the bit pattern of the character itself. These outputs are therefore somewhat longer than the normal 35 string code. In a manner to be described, this variation in output length is avoided by initializing the string table to contain all single character strings before input data is processed. This approach simplifies the implementation complexity in that it eliminates any bit shift- 40 ing hardware otherwise required but may reduce compression. Reduction in compression occurs because the codes assigned to unused single characters cannot be profitably utilized, but expand the number of bits required to distinguish all assigned codes. This reduction 45 in compression only occurs during compression of initial strings utilizing variable length codes.

In the embodiments of the invention to be described hereinbelow, the decompression process is implemented with logically the same string table as the compression 50 process but stored somewhat differently. When each code signal is received by the decompressor, it is looked up directly in the string table where it is translated into a prefix string code and an extension character. The prefix code is then looked up and translated, and the 55 process is repeated until the empty string is encountered. This process, however, produces data characters in the reverse order from the sequential order with which that character string was received by the compressor. Two techniques are described hereinbelow for 60 reversing the intra-string character sequence. A LIFO stack (last-in-first-out) is utilized to temporarily hold the characters and as each character is produced by the decompressor, it is pushed onto the stack. At the end of the iteration, the characters are read from the stack in 65 correct order. Alternatively, a string length count is maintained for each code in the string table so that when a character is read out, it can be placed directly in

10

the appropriate position in a random-access output

FIGS. 2 and 3 illustrate a compressor and decompressor, respectively, for implementing a highest performance embodiment of the present invention. This embodiment provides an economical and fast compression process. A character size of B bits and a compressor code size of C bits is utilized. The string table contains 2<sup>C</sup> locations. Typically, B is 8 bits and C is 12 bits with other character and code sizes being utilizable in practicing the invention. This embodiment utilizes a fixed length code symbol signal of C bits which is utilized as the address of the string entry in the hashed string table. The first  $2^B$  locations are initialized to contain the single character strings. The compressor utilizes a string table which contains in each entry only the C-bit prefix string code. The decompression table contains this same code and in addition, the B-bit extension character appended to the prefix string to compose the current string.

The addresses into the string table, which are utilized as the output code symbol signals from the compressor are derived utilizing a hash function that will be described in detail subsequent to the description of the embodiments of FIGS. 2 and 3. The hash function generates N C-bit addresses in sequence. The embodiments of FIGS. 2 and 3, as well as those of FIGS. 4 and 5 utilize a controller to control the numerous functions described herein below. For example, the hash function device notifies the controller upon the occurance of the N<sup>TH</sup> address. The hardware embodiments of the invention are implemented and described as sequential state machines. The controllers of the compressor and decompressor receive signals from the various blocks thereof and provide signals thereto to control the components of the compressor and decompressor in accordance with the extant state of the machine. Any standard control logic system may be utilized to control the described sequences. For example, one flip-flop per state may be activated to distinguish the operative connections and functions to be performed during each state with the flip-flop controlling the state being activated during that state.

Referring now to FIG. 2, the compressor of the highest performance embodiment of the present invention is illustrated. The compressor receives input character signals on a bus 10 and provides compressed output code signals on a bus 11. The input characters are provided on the bus 10 from external equipment. The external equipment also provides a data availale signal on a line 12 whenever an input character signal is available from the external equipment and applied on the bus 10. The data available signal on the line 12 is applied to a compressor controller 13. The compressor controller 13 provides control signals to all of the blocks of the compressor of FIG. 2 via leads 14. The compressor controller 13 sequences the compressor of FIG. 2 through the control states in a manner to be described in detail hereinbelow. The controller 13 also provides a character strobe signal to the external equipment on a line 15 to call for additional input characters. When an output code signal is available on the bus 11, the controller 13 provides a code strobe signal to the external equipment on a lead 16.

The input characters on the bus 10 are entered into a B-bit character register 17. In order to create single character string codes, the B-bit character byte from the character register 17 is inserted via a bus 18 into the B least significant bits of a C-bit code number register 19.

The high order C-B bits of the code number register 19 may be set to zero by means of a control signal on a lead 20

The code symbol signal from the register 19 and the character signal from the register 17 are applied via 5 busses 21 and 22 respectively to a hash function circuit 23. The hash function circuit 23 combines the C-bit code signal on the bus 21 with the B-bit character on the bus 22 to provide N C-bit addresses sequentially on a bus 24. The hash function circuit 23 signals the controller 13 via a lead 25 if the hash address provided on the bus 24 is the N<sup>TH</sup> address in the sequence.

The hash function circuit 23 also receives a New Hash command and a Next Hash command from the controller 13. The controller 13 commands the hash 15 function circuit 23 to provide the first of the N hash addresses in response to the New Hash command and the subsequent hash addresses in response to subsequent occurrances of the Next Hash command. As described, when the hash function circuit 23 has provided the N<sup>TH</sup> 20 hash address, a signal is returned to the controller 13 via the lead 25.

The hash addresses on the bus 24 are applied to a comparator 26 which also receives a constant value signal equal to  $2^B$ . The comparator 26 compares the 25 hash address on the bus 24 with the value  $2^B$  and provides a signal to the controller 13 via a lead 27 indicating whether the hash address on the bus 24 is greater than  $2^B$  or is less than or equal to  $2^B$ .

The hash address on the bus 24 is also applied to a 30 C-bit RAM address register 28. An address loaded into the RAM address register 28 accesses a RAM 29 utilized to store the compressor string table. The RAM 29 contains 2<sup>C</sup> C-bit locations. Each string is stored in the RAM 29 by storing its prefix code at a location addressed by the code assigned to the string. The code assigned to the string is derived by hashing the prefix code with the string extension character in a manner to be described.

The RAM 29 receives a READ command and a 40 WRITE command from the controller 13 to control the READ and WRITE functions of the RAM 29. The RAM 29 is controlled by the controller 13 to receive either a C-bit value equal to  $2^B$  or the C-bit code number signal from the register 19 via a bus 30. In accordance 45 with the application of the WRITE command to the RAM 29, either the constant value  $2^B$  or the code number on the bus 30 is written into the location accessed by the RAM address in the register 28 in accordance with control signals from the controller 13. The RAM 29 50 also provides in response to the READ command, the C-bit contents of the accessed location on a bus 31. The RAM output on the bus 31 and the output of the code register 19 are applied as inputs to a comparator 32. The comparator 32 also receives a constant value signal 55 equal to  $2^B$ . The comparator 32 compares the output of the RAM 29 with the output of the code number register 19 and with  $2^B$ . The results of the comparison are provided to the controller 13 via a lead 33. The comparison signal on the lead 33 indicates to the controller 13 60 whether the RAM output on the bus 31 is equal to the code number from the register 19 or to  $2^B$  or to neither. For reasons to be later described, the controller 13 controls the RAM address register 28 to transfer its contents to the code number register 10 via a bus 34.

The compressor of FIG. 2 also includes an initialization counter 35 that provides a C-bit signal to the RAM address register 28 via a bus 36. The counter 35 may be set to zero via a zero valued signal applied thereto. The controller 13 controls the counter 35 via a count command to add one to the contents of the counter for each application of the count command. The counter 35 signals the controller 13 when it has attained the count  $2^C$  via a carry-out or overflow signal on a lead 37. The initialization counter 35 is utilized to initialize the RAM 29 to empty by sequentially accessing all of the locations thereof and writing in the constant value  $2^B$  selected to indicate the empty condition.

The basic operation of the compressor of FIG. 2 is capsulized as follows:

1. Initialize RAM to empty, for each data block

On first character of each byte string: character—code register, as first code number

3. On successive characters:

hash (code, character)—sequence of N RAM addresses; for each location in sequence

If RAM output = code: RAM address → code register; reenter this step with another character.

If RAM location is empty: write code register→

RAM: transmit code value as output; go to step

2

else, after all hash address:transmit code value as output; go to step 2.

With continued reference to FIG. 2, the following is a state machine description of the compressor of FIG. 2. State 0: Wait state, at beginning of each data block Set initialization counter to zero.

Wait for data available signal: go to State 1

State 1: Initialize RAM

initialization counter-RAM address

$2^B \rightarrow RAM$  data input

write RAM

add +1 to initialization counter

If initialization counter  $>2^C$  repeat State 1 else go to State 2.

State 2: Read first character of block for starting code Input character—code register (low-order B bits)

Zeros—code register (high order C-B bits) go to State 3.

State 3: Process next character in this string

Read next character

If no new input characters available: transmit code register—output; go to State 0

hash (code register, next character) $\rightarrow$ RAM address If RAM address  $\leq 2^{B}$ : go to State 4

Read RAM

If (RAM output)=(code register): RAM address→code register; go to State 3

If (RAM location)= $2^B$ : go to State 5

Else: go to State 4

State 4: Continue Search

next hash (code, character)→RAM address

If RAM address  $\leq 2^{B}$ : If last hash value: go to State 6

Else: repeat State 4

Read RAM

If (RAM output)=(code register): RAM address→code register; go to State 3

If (RAM output)= $2^B$ : go to State 5

Else: If last hash iteration: go to State 6 else repeat State 4

State 5: Create new string

Write (code register)→RAM go to State 6

State 6: End of String

Transmit (code register)→output

Character register-code register (low-order B bits)

Zeros=code register (high-order C-B bits) go to State 3

A more detailed description of the operation of the compressor of FIG. 2 with respect to the state machine description given above is now provided:

[0]. Wait State. While waiting for a block of input characters, the compressor of FIG. 2 resides in this state. During the Wait State, the controller 13 resets the initialization counter 35 to zero. The data available signal on the lead 12 from the external source which 10 supplies the input data is utilized to indicate when input data is available. When data becomes available, the data available signal on the lead 12 signals the controller 13 to enter the Initialization State.

[1]. Initialization State. The contents of the Random 15 Access Memory, RAM, 29, are initialized to be empty. The empty symbol is arbitrarily chosen as  $2^B$  for implementation convenience. Thus, in the Initialization State, the value  $2^B$  is written into each location of the memory 29. The empty symbol should never be assigned to a 20 string code. The locations zero through  $2^B$  are initialized to empty for implementation convenience although they will never be accessed. Conceptually, the locations zero through  $2^B-1$  are initialized to contain the  $2^B$ single character string which are preassigned code val- 25 ues equal to the characters they represent. Thus, the  $2^B$ single character strings are preassigned code values zero through  $2^{B}-1$ . The initialization is achieved in repeated memory cycles, by gating the value in the C bit initialization counter 35 via the bus 36 to the RAM 30 address register 28. The input to the RAM 29 is selected from the C bit constant input value  $2^B$ . The RAM 29 has 2<sup>C</sup> locations each C bits wide. The RAM 29 is controlled to write the selected input data into the location designated by the RAM address register 28. The initial- 35 ization counter 35 is commanded to count up by adding 1 to its present contents. This sequence of events is repeated  $2^C$  times, once for each memory location. After  $2^{C}$  such counts, the initialization counter 35 provides an overflow or carry-out signal to the controller 40 13 via the lead 37 signalling that the  $2^{C}$  counts have occurred. This causes the compression unit of FIG. 2 to advance to the First Character State.

[2]. First Character State. After the initialization, the compressor of FIG. 2 reads the first input character 45 residing on the bus 10 gating the B bits thereof into the B bit character register 17. A signal is then provided by the controller 13 on the character strobe line 15 to cause the next input character signal to be provided on the input bus 10 by the external equipment. The B character 50 bits in the character register 17 are then gated via bus 18 into the least significant (right-hand) B bits of the C bit code number register 19 and the most significant C-B bits of the register 19 are set to zero. This procedure converts the first input character into the preassigned 55 code value for that single character string. In the embodiment of FIG. 2, the  $2^B$  preassigned code values are equal to the characters of the alphabet respectively, that they represent. Having initiated the first string the Next Character State is entered which is the main cycle of the 60 iterations of the compressor of FIG. 2.

[3]. Next Character State. Upon entering this state, a valid character string has been parsed from the input and its code value resides in the code number register 19. The next character is now read from the bus 10 into 65 the character register 17 and the character strobe signal on the line 15 is returned to the external data source. In the event that the data available signal on the line 12

14

indicates that no such character was available on the bus 10, then the compressor has attained the end of the data block. In that situation, the code value for the last data string, residing in the code register 19 is transmitted as output code on bus 11 and the code strobe signal on the line 16 is sent to the external equipment indicating that a new compressed code signal is being provided. The controller 13 then returns the compressor to the Wait State.

If, however, the end of the data block has not been attained and a new character was available and entered into the character register 17, this B bit character via the bus 22 is combined, in the hash function circuit 23, with the C bit code number in the register 19 provided on the bus 21. Under control of the new hash command from the controller 13, the hash function circuit 23 provides the first RAM address for this code, character combination. This hash address on the bus 24 is compared to the value  $2^B$  by the comparator 26. If the hash address on the bus 24 is less than or equal to  $2^B$ , then this location is inaccessible and the next hash address is selected by going to the Next Hash State. Address values less than or equal to  $2^B$  are not permitted as new code values because the values less than  $2^B$  are preassigned to be the code values for the single character strings and the value  $2^B$  was preassigned to identify an empty memory location (an unused code value).

If the hash address is greater than  $2^B$ , the normal case, then the hash address on the bus 24 is gated into the RAM address register 28 and the RAM 29 is controlled to read the contents of that address. The C bit result on the bus 31 is compared in comparator 32 to both the code value from the register 19 and to the value  $2^B$ . If the output of the RAM 29 on the bus 31 is equal to the code number from the register 19, then the extended string has been previously encountered and already assigned a code value; viz, the RAM address value of the location just read. The new code number is gated from the RAM address register 28 via the bus 34 to the code number register 19 and this Next Character State is reentered to repeat the procedure on a new character.

Alternatively, if the RAM output on the bus 31 is equal to  $2^B$  then this location is empty, signifying that the extended string is not in the table and so cannot be utilized to parse the input data. This terminates the building of the current string and the New String State is now entered.

In the event, however, that the RAM output on the bus 31 equals neither  $2^B$  nor the code number from the register 19 other locations in the RAM 20 must be searched, which is performed in the Next Hash State.

[4]. Next Hash State. In this state, a further RAM address is generated by the hash function circuit 23 for the current code, character combination under control of the Next Hash command from the controller 13. The procedures of the previous state are then essentially duplicated. The new address is compared by the comparator 26 to 2<sup>B</sup> and if the address is not greater than 2<sup>B</sup> it is not utilized. In this event, this Next Hash State is reentered to obtain another address. If all N hash addresses have been examined, as indicated by a signal from the hash function circuit 23 on the lead 25, then the current string is considered as not existing in the string table and there is no space to enter it. The String End State is then entered.

If, however, the hash address is greater than  $2^B$ , the address on the bus 24 is gated to the RAM address register 28 and the RAM 29 is controlled to read the

contents at that location. The result provided on the RAM output bus 31 is compared in the comparator 32 to the code number in the register 19 and to  $2^B$ . If the RAM output equals the code number, then the new code number from the RAM address register 28 is gated via the bus 34 to the register 19 and the Next Character State is entered. Alternatively, if the RAM output on the bus 31 equals the value  $2^B$ , then the New String State is entered. If the RAM output on the bus 31 equals neither  $2^B$  nor the code value, then this process is repeated up to N times by reentering this Next Hash State for a new address value. When N locations have been tried, as indicated by a signal from the hash function circuit 23 on the lead 25, the string is terminated and the String End State is entered.

[5]. New String State. The encountering of an empty location in the string table indicates that the searched for extended string has not been found in the table and that it should be entered therein. This is accomplished by writing the prefix code number of the extended 20 string into the RAM 29 thus reserving the assigned address as the code value for the extended string. Accordingly, the address in the RAM address register 28 is maintained at its former value and the RAM 29 is controlled to write the contents of the code number register 25 19 via the bus 30 into the addressed location. The String End State is then entered.

[6]. String End State. When entering this state, it had been determined that the extended string was not in the string table and so the existing string code should be 30 transmitted as output and a new string begun. Accordingly, the output code signal from the code number register 19 is transmitted on the output bus 11 and the Code Strobe Signal is sent via the lead 16 to notify the external apparatus that a new compressed code signal is 35 present on the bus 11. The precise form of this interface will vary according to the specific requirements of the external apparatus that receives the compressed data signals. The new string is initiated utilizing the existing character in the character register 17 which is translated 40 into its preassigned single character string code by gating it into the least significant B-bits of the code number register 19 via the bus 18 and placing zeros in the higher C-B bit positions of the register 19. The Next Character State is reentered to construct the new string.

Referring now to FIG. 3, a decompressor for recovering the data character sequences corresponding to the compressed code signals from the compressor of FIG. 2 is illustrated. The decompressor of FIG. 3 is implemented so that the output thereof may be placed di- 50 rectly into an external random access buffer, which arrangement provides rapid reversal of the output character strings. This decompressor embodiment utilizes explicit management of output location addresses. Each entry in the string table contains a "level" value which 55 indicates the number of characters in the prefix string. This level value is utilized to achieve proper positioning of each character in the output buffer. The external equipment which receives the decompressed character strings from the decompressor is assumed to utilize a 60 random access memory to store the data. When utilizing an external random access buffer, the decompressor provides an address with each output data character, which address defines the location of that character in the output string. The initial location corresponds to an 65 address of zero. The external equipment may manipulate the location addresses to match its particular memory addressing requirements.

The decompressor of FIG. 3 provides output characters in a different order than they were received by the compressor of FIG. 2, but by providing a location value with each character, the final assembled data stream will be in the correct sequence. If a random access memory is not utilized in the external equipment, a stack mechanism approach to string reversal, such as that described below, with respect to FIG. 5 may be utilized.

The decompressor of FIG. 3 receives compressed code signals on a bus 50 and provides corresponding strings of recovered data character signals on a bus 51. The compressed code signals are provided on the bus 50 from external equipment. The external equipment also provides a data available signal on a line 52 whenever a compressed code signal is available from the external equipment and applied on the bus 50. The data available signal on the line 52 is applied to a decompressor controller 53. The controller 53 provides control signals to all of the blocks of the decompressor of FIG. 3 via leads 54. The decompressor controller 53 sequences the decompressor of FIG. 3 through the control states thereof in a manner to be described in detail hereinbelow. The controller 53 also provides an input data strobe signal to the external equipment on a line 55 to call for additional input code signals. When an output character is available on the bus 51, the controller 53 provides an output data strobe signal to be external equipment on a lead 56.

The compressed code signals on the bus 50 are entered into a C-bit code register 57. In order to distinguish between codes representative of single character strings and codes representative of multiple character strings, the output of the code register 57 is compared to a constant value signal of  $2^B$  in a comparator 58. Accordingly, the comparator 58 provides a signal to the controller 53 via a lead 59 indicative of whether the code signal in the register 57 is greater or less the  $2^{B}$ . When the code value in the register 57 is less than  $2^{B}$ , and therefore representative of a single character string, the low order B-bits of the register 57 are transferred via a bus 60 to a B-bit last character register 61. Since as discussed above, the code value for a single character string is the same as the character, the single character 45 string transferred to the last character register 61 via the bus 60 is output directly on the bus 51.

When the compressed code signal in the register 57 is greater than  $2^B$ , as determined by the comparator 58, the code value in the register 57 is transferred to a RAM address register 62 via a bus 63. At certain times during the decompression of compressed code signals, the compressed code in register 57 is transferred to a C-bit code register 64 via a bus 65 to save the value for later processing. Under certain conditions, to be later described, the code value in the register 64 may be transferred to the RAM address register 62 via a bus 66.

In order to provide appropriate addresses for the storage of character strings in the decompressor, the character signal stored in the last character register 61 and the code signal stored in the code register 64 are applied via busses 67 and 68, respectively, to a hash function circuit 69. The hash function circuit 69 is identical to the hash function circuit 23 described above with respect to FIG. 2. The hash function circuit 69 combines the C-bit code signal on the bus 68 with the B-bit character signal on the bus 67 to provide N C-bit addresses sequentially to the RAM address register 62 via a bus 70. The hash function circuit 69 signals the

controller 53 via a lead 71 if the hash address provided on the bus 70 is the  $N^{TH}$  address in the sequence.

The hash function circuit 69 also receives a New Hash command and a Next Hash command from the controller 53. The controller 53 commands the hash 5 function circuit 69 to provide the first of the N hash addresses in response to the New Hash command and the subsequent hash addresses in response to subsequent occurrences of the Next Hash command. As described when the hash function circuit 60 has provided the N<sup>TH</sup> 10 hash address, a signal is returned to the controller 53 via the lead 71.

The RAM address from the RAM address register 62 is applied to a comparator 72 and to the last character register 61 via a bus 73. The comparator 72 also receives 15 a constant value signal equal to  $2^B$ . The comparator 72 compares the RAM address on the bus 73 with the value  $2^B$  and provides a signal to the controller 53 via a lead 74 indicating whether the address on the bus 73 is greater than or less than  $2^B$ . When it is less than  $2^B$ , the 20 value in the RAM address register 62 is applied to the last character register 61 to recover the first character in a character string in a manner to be described.

An address loaded into the RAM address register 62 accesses a RAM 75 utilized to store the decompressor 25 string table. The RAM 75 contains 2<sup>C</sup> locations each being C+B+L bits wide. Each string is stored in the RAM by storing its C bit prefix code, its B bit extension character and an L bit level value. The value in the level field is equal to the number of bits in the prefix of the 30 string. Each string is stored in the RAM 75 at a location addressed by the code assigned to the string. The code assigned to the string is derived by hashing the prefix code with the string extension character in a manner to be described.

The RAM 75 receives a READ command and a WRITE command from the controller 53 to control the READ and WRITE functions of the RAM 75. For initialization purposes in a manner to be explained, the RAM 75 receives constant value signals 2<sup>B</sup>, zero and 40 zero for writing into the prefix code, character and level fields of the RAM location addressed by the RAM address register 62. These values are applied under control of the controller 53 and are entered upon application of the WRITE command. The RAM 75 is also 45 controlled by the controller 53 to selectively receive the code value from the code register 64 via a bus 76, the character value from the last character register 61 via a bus 77 and a level value from a level register 78 via a bus 79 for entry into the prefix, character and level fields 50 respectively of the RAM location addressed by the RAM address register 62. These values are written into the respective fields in response to the WRITE command from the controller 53.

The controller 53 also controls the RAM 75 in response to the READ command to provide on a bus 80 ing all of the location at the prefix code value stored in the prefix code field of the RAM location addressed by the RAM address register 62. This code value on the bus 80 is applied to the RAM address register 62 as well as to a detector 81. The 60 capsulized as follows: detector 81 determines whether or not the prefix code on the RAM output 80 is equal to  $2^B$  and provides a signal to the controller 53 via a lead 82 accordingly.

The controller 53 also controls the RAM 75 to selectively provide the character value from the character 65 field via a bus 83 to the last character register 61. The character value is provide on the bus 83 fron the character field of the RAM location addressed by the RAM

18

address register 62 in response to the READ command. In a similar manner, the controller 53 controls the RAM 75 to provide the level value via a bus 84 either to a level register 85 or to an address adder 86. The level value is applied to the bus 84 from the level field of the RAM location accessed by the RAM address register 62. The selective routing of the level value on the bus 84 to the level register 85 and the address adder 86 is controlled by the controller 53 in accordance with the extant state of the decompressor.

The decompressor of FIG. 3 includes apparatus for assigning addresses to the output character signals for proper alignment in an external random access memory. Accordingly, the address adder 86 provides such location address to the external equipment on a bus 87. The address adder 86 receives inputs from an outpointer register 88, the level value from the RAM 75 on the bus 84 and the level value from the level register 78 on a bus 89. The address adder 86 also receives a zero value signal on a bus 90. The controller 53 controls the address adder 86 to add either the level value on the bus 84, the level value on the bus 89, or the level value on the bus 90 to the value in the outpointer register 88 in accordance with the extant state of the decompressor and logical conditions existing during the state in a manner to be described. The result of the addition provides the location address on the bus 87.

The output of the address adder 86 is also applied as an input to the outpointer register 88. The controller 53 controls the outpointer register 88 to replace the extant outpointer value with the result of an addition in the adder 86 or merely to provide a base address to the adder 86 for generating location addresses on the bus 87. The controller 53 also controls the level registers 78 and 85 to transfer the level value from the level register 85 to the level register 78 increasing the value by one via an adder 91 in the transfer path. Additionally, the controller 53 controls the level registers 78 and 85 to transfer the contents of the level register 78 to the level register 85 via a bus 92. The apparatus also includes inputs to the level register 85 and the outpointer register 88 to zero these registers under conditions to be described.

The decompressor of FIG. 3 also includes an initialization counter 93 that provides a C-bit signal to the RAM address register 62 via a bus 94. The counter 93 may be set to zero via a zero-valued signal applied thereto. The controller 53 controls the counter 93 via Count command to add one to the contents of the counter for each application of the Count command. The counter 93 signals the controller 53 when it has attained the count  $2^C$  via a carry-out or overflow signal on a lead 95. The initialization counter 93 is utilized to initialize the RAM 75 to empty by sequentially accessing all of the locations thereof and writing in the constant values  $2^B$ , zero and zero into the prefix code, character and level fields respectively.

The basic operation of the decompressor of FIG. 3 is capsulized as follows:

- 1. Initialize RAM to empty, for each data block

- 2. For each input code, read code→code register; save certain data from prior code for string table update.

- Code register—RÂM address Read RAM producing prefix code, extension character, string length

- If prefix  $code \ge 2^B$ , characater—output at location determined by string length; prefix code—code register; repeat step 3

```

If prefix code \langle 2^B; code value—output as character;

go to step 4

4. At end of character string update string table:

Write prior received code and last output character

into first empty location from sequence produced 5

by hash (prior code, last character); go to step 2.

With continued reference to FIG. 3, the following is

a state machine description of the decompressor of FIG.

State 0: Wait State, at beginning of each data block

initialization counter=zero

outpointer=zero

wait for data available signal; go to State 1

State 1: Initialize RAM

initialization counter-RAM address

2^B, zero, zero\rightarrowRAM input

write RAM

add +1 to initialization counter

If initialization counter < 2^C repeat State 1; else go to

State 2

State 2. Process initial input code

Input code symbol—code register 1

Input data strobe

Code value (low order B bits)-last character regis-

Location Address=outpointer; output data strobe

Level Register 1=zero

go to State 3

State 3: Next input code

Code register 1→code register 2

(Level reg. 1)+1\rightarrowlevel register 2

(Level reg. 2)+(outpointer)→outpointer

If no new input available; go to State 0

Read input code value →code reg. 1

Input data strobe

If code reg. 1 \ge 2^B:

Level Reg. 1=0

code register 1-RAM address

go to State 4

If code reg. 1 < 2^B:

Code value (low order B bits of code reg. 1)→last

character reg.

Location Address=outpointer; output data strobe

go to State 5

State 4: First character cycle

Read RAM

If code (RAM\neq 2^B [normal case]

level (RAM)→level reg. 1

code (RAM)→RAM address

char (RAM)→last char. reg.

Location address=outpointer+level (RAM); output

data strobe

If code (RAM)=2^B [an abnormal case]

level reg. 2→level reg. 1

code reg. 2→RAM address

Location address=outpointer+level reg. 2; output

data strobe

go to State 5

State 5: Later character cycles

If RAM address \geq 2^B: Read RAM

code (RAM)→RAM address

char (RAM)-last char. reg.

Location address = outpointer + level (RAM); output

data strobe

go to State 5

```

If RAM address  $< 2^B$ :

RAM address (low B bits)-last char. reg.

Location address=outpointer: output data strobe

```

20

go to State 6

State 6: Update string table

Hash (code register 2, last char. reg.)→RAM address

Read RAM

If code (RAM)=2^B and if RAM address>2^B:

go to State 7

Else: Repeat State 6 with new hash value If this was

last hash, go to State 3

State 7: Write Cycle

with RAM address unchanged

code reg. 2→code (RAM)

last char. reg.--char (RAM)

level reg. 2→level (RAM)

Write RAM

go to State 3

A more detailed description of the operation of the

decompressor of FIG. 3 with respect to the state ma-

chine description given above is now provided.

[0.] Wait State. While waiting for a block of com-

20 pressed input code signals, the decompressor of FIG. 3

resides in this state. During the Wait State, the control-

ler 53 resets the initialization counter 93 to zero. The

controller 53 also resets the outpointer register 88 to

zero so that subsequent transfers of output character

signals to the external output memory begins at the

lowest available address. The data available signal on

the lead 52 from the external source which supplies the

input code, is utilized to indicate when input code is

available. When input code becomes available, the data

30 available signal on the lead 52 signals the controller 53

to enter the Initialization State.

[1.] Initialization State. The contents of the random

access memory, RAM, 75 are initialized to be empty.

The RAM 75 contains three distinct data fields in each

35 of its 2<sup>C</sup> locations; viz. a prefix code value of C bits, an

extension character of B bits, and a level value of L bits.

Each location corresponds to a string of characters

where the address of the location is the code value of

the string and the contents of the location provide the

composition of the string in terms of its prefix string and

extension character. The level field provides the num-

ber of characters in the prefix string and is utilized in

locating output characters in the appropriate positions

in the output sequence. L bits are provided for the level

45 value under the assumption that no string length will

exceed 2^L characters where L is less than or equal to C.

All of the locations of the RAM 75 are initialized by

```